CODE TIME TECHNOLOGIES

# Abassi RTOS

# Porting Document ARM Cortex-M4 – Keil Suite

**Copyright Information**

This document is copyright Code Time Technologies Inc. ©2012. All rights reserved. No part of this document may be reproduced or distributed in any form by any means, or stored in a database or retrieval system, without the written permission of Code Time Technologies Inc.

Code Time Technologies Inc. may have patents or pending applications covering the subject matter in this document. The furnishing of this document does not give you any license to these patents.

#### Disclaimer

Code Time Technologies Inc. provides this document "AS IS" without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

Code Time Technologies Inc. does not warrant that the contents of this document will meet your requirements or that the document is error-free. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the document. Code Time Technologies Inc. may make improvements and/or changes in the product(s) and/or program(s) described in the document at any time. This document does not imply a commitment by Code Time Technologies Inc. to supply or make generally available the product(s) described herein.

$\mu$ Vision is a registered trademark of Keil Elektronik GmbH / Keil Software Inc. ARM and Cortex are registered trademarks of ARM Limited. All other trademarks are the property of their respective owners.

### **Table of Contents**

| 1 | IN           | TRODUCTION                                                             | 6  |

|---|--------------|------------------------------------------------------------------------|----|

|   | $1.1 \\ 1.2$ | DISTRIBUTION CONTENTS<br>LIMITATIONS                                   |    |

|   |              |                                                                        |    |

| 2 | TA           | ARGET SET-UP                                                           | 7  |

|   | 2.1          | OS_STACK_SIZE / OS_HEAP_SIZE SET-UP                                    |    |

|   | 2.2          | INTERRUPT STACK SET-UP                                                 |    |

|   | 2.3          | SATURATION BIT SET-UP                                                  |    |

|   | 2.4          | FPU SET-UP                                                             | 12 |

| 3 | IN           | TERRUPTS                                                               | 15 |

|   | 3.1          | INTERRUPT HANDLING                                                     | 15 |

|   | 3.1          |                                                                        |    |

|   | 3.1          |                                                                        |    |

|   | 3.2          | INTERRUPT PRIORITY AND ENABLING                                        |    |

|   | 3.3          | FAST INTERRUPTS                                                        |    |

|   | 3.4          | NESTED INTERRUPTS                                                      |    |

| 4 | ST           | ACK USAGE                                                              | 22 |

| 5 | SE           | CARCH SET-UP                                                           | 23 |

| 6 | CH           | HP SUPPORT                                                             | 26 |

| 7 | M            | EASUREMENTS                                                            | 27 |

|   | 7.1          | Memory                                                                 |    |

|   | 7.2          | LATENCY                                                                |    |

| 8 | AF           | PPENDIX A: BUILD OPTIONS FOR CODE SIZE                                 |    |

|   | 8.1          | Case 0: Minimum build                                                  | 34 |

|   | 8.2          | CASE 0: MINIMUM BULD                                                   |    |

|   | 8.3          | CASE 2: + MULTIPLE TASKS AT SAME PRIORITY                              |    |

|   | 8.4          | CASE 3: + PRIORITY CHANGE / PRIORITY INHERITANCE / FCFS / TASK SUSPEND |    |

|   | 8.5          | CASE 4: + TIMER & TIMEOUT / TIMER CALL BACK / ROUND ROBIN              |    |

|   | 8.6          | CASE 5: + EVENTS / MAILBOXES                                           |    |

|   | 8.7          | CASE 6: FULL FEATURE BUILD (NO NAMES)                                  |    |

|   | 8.8          | CASE 7: FULL FEATURE BUILD (NO NAMES / NO RUNTIME CREATION)            |    |

|   | 8.9          | CASE 8: FULL BUILD ADDING THE OPTIONAL TIMER SERVICES                  | 42 |

# List of Figures

| 7 |

|---|

| 3 |

| ) |

| ) |

|   |

| 2 |

| 3 |

| 5 |

| 7 |

| 7 |

| ) |

|   |

## List of Tables

| TABLE 1-1 DISTRIBUTION                                                   | 6  |

|--------------------------------------------------------------------------|----|

| TABLE 2-1 OS         STACK         SIZE AND OS         HEAP         SIZE | 8  |

| TABLE 2-2 COMMAND LINE SET OF HEAP AND STACK SIZES                       |    |

| TABLE 2-3 OS ISR STACK                                                   | 10 |

| TABLE 2-4 COMMAND LINE SET OF OS_ISR_STACK                               |    |

| TABLE 2-5 SATURATION BIT CONFIGURATION                                   | 11 |

| TABLE 2-6 COMMAND LINE SET OF SATURATION BIT CONFIGURATION               | 11 |

| TABLE 2-7 COMMAND LINE ENABLING OF THE FPU                               | 12 |

| TABLE 2-8 FPU RUN TIME ON / OFF CONFIGURATION                            | 13 |

| TABLE 2-9 COMMAND LINE SET OF OS_FPU_ON_OFF                              | 13 |

| TABLE 3-1 ABASSI CORTEXM4 KEIL.S INTERRUPT TABLE SIZING                  | 15 |

| TABLE 3-2 COMMAND LINE SET THE INTERRUPT TABLE SIZE                      | 16 |

| TABLE 3-3 OVERLOADING THE INTERRUPT TABLE SIZING FOR ABASSI.C            |    |

| TABLE 3-4 ATTACHING A FUNCTION TO AN INTERRUPT                           | 17 |

| TABLE 3-5 INVALIDATING AN ISR HANDLER                                    | 18 |

| TABLE 3-6 DISTRIBUTION INTERRUPT TABLE CODE.                             | 19 |

| TABLE 3-7 STM32F407 UART 1 / 2 FAST INTERRUPTS                           | 19 |

| TABLE 3-8 FAST INTERRUPT WITH DEDICATED STACK                            | 20 |

| TABLE 3-9 REMOVING INTERRUPT NESTING                                     | 21 |

| TABLE 3-10 PROPAGATING INTERRUPT NESTING                                 | 21 |

| TABLE 4-1 CONTEXT SAVE STACK REQUIREMENTS                                | 22 |

| Table 5-1 Search Algorithm Cycle Count                                   | 24 |

| TABLE 7-1 "C" CODE MEMORY USAGE                                          | 28 |

| Table 7-2 Assembly Code Memory Usage                                     | 28 |

| TABLE 7-3 MEASUREMENT WITHOUT TASK SWITCH                                | 30 |

| TABLE 7-4 MEASUREMENT WITHOUT BLOCKING                                   | 30 |

| TABLE 7-5 MEASUREMENT WITH TASK SWITCH                                   | 30 |

| TABLE 7-6 MEASUREMENT WITH TASK UNBLOCKING                               | 31 |

| TABLE 7-7 LATENCY MEASUREMENTS FPU OFF                                   |    |

| TABLE 7-8 LATENCY MEASUREMENTS FPU ON                                    | 33 |

| TABLE 8-1: CASE 0 BUILD OPTIONS                                          |    |

| TABLE 8-2: CASE 1 BUILD OPTIONS                                          | 35 |

| TABLE 8-3: CASE 2 BUILD OPTIONS                                          |    |

| TABLE 8-4: CASE 3 BUILD OPTIONS                                          |    |

| TABLE 8-5: CASE 4 BUILD OPTIONS                                          | 38 |

| TABLE 8-6: CASE 5 BUILD OPTIONS                                          |    |

| TABLE 8-7: CASE 6 BUILD OPTIONS                                          |    |

| TABLE 8-8: CASE 7 BUILD OPTIONS                                          |    |

| TABLE 8-9: CASE 8 BUILD OPTIONS                                          | 42 |

|                                                                          |    |

### 1 Introduction

This document details the port of the Abassi RTOS to the ARM Cortex-M4 processor The software suite used for this specific port is the MDK-ARM Microcontroller Development Kit, more commonly known as Keil  $\mu$ Vision4; the version used for the port and all tests is V4.50.0.

### **1.1 Distribution Contents**

The set of files supplied with this distribution are listed in Table 1-1 below:

| File Name                | Description                                                                 |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| Abassi.h                 | Include file for the RTOS                                                   |  |  |  |  |

| Abassi.c                 | RTOS "C" source file                                                        |  |  |  |  |

| Abassi_CORTEXM4_KEIL.s   | RTOS assembly file for the ARM Cortex-M4 to use with the Keil $\mu Vision4$ |  |  |  |  |

| Demo_1_STM32_P407_KEIL.c | Demo code that runs on the Olimex STM32-P407 evaluation board               |  |  |  |  |

| Demo_3_STM32_P407_KEIL.c | Demo code that runs on the Olimex STM32-P407 evaluation board               |  |  |  |  |

| Demo_5_STM32_P407_KEIL.c | Demo code that runs on the Olimex STM32-P407 evaluation board               |  |  |  |  |

| Demo_7_STM32_P407_KEIL.c | Demo code that runs on the Olimex STM32-P407 evaluation board               |  |  |  |  |

| AbassiDemo.h             | Build option settings for the demo code                                     |  |  |  |  |

#### **Table 1-1 Distribution**

### 1.2 Limitations

To optimize reaction time of the Abassi RTOS components, it was decided to require the processor to always operate in privileged mode (which is the default start-up mode for Cortex-M microcontrollers) and to always use the main stack pointer (MSP). The start-up code supplied in the distribution fulfills these constraints and one must be careful to not change these settings in the application.

The SVCall interrupt (interrupt number -5 / interrupt vector number 11) is not available as it is reserved for the OS, and the Abassi RTOS uses it.

### 2 Target Set-up

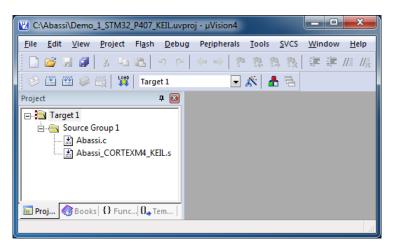

Very little is needed to configure the Keil  $\mu$ Vision4 development environment to use the Abassi RTOS in an application. All there is to do is to add the files Abassi\_c and Abassi\_CORTEXM4\_KEIL.s in the source files of the application project, and make sure the three configuration settings in the file Abassi\_CORTEXM4\_KEIL.s (OS\_STACK\_SIZE as described in Section 2.1, OS\_ISR\_STACK as described in Section 0, OS\_HANDLE\_PSR\_Q as described in Section 2.3, OS\_FPU\_ON\_OFF described in Section 2.4) are set according to the needs of the application. As well, update the include file path in the C/C++ compiler preprocessor options with the location of Abassi.h. There is no need to include a start-up file, as the Abassi\_CORTEXM4\_KEIL.s file contains all the start-up operations.

Figure 2-1 Project File List

| 😵 ARM Development Tools                                                                                                                         |                                                                                |                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hide Locate Back Forward Print                                                                                                                  | Diff-                                                                          |                                                                                                                                                                                                                                                                                                                                                  |

| Contents     Index     Search     Favorites       Type in the word(s) to search for:       _mutex      ist Topics     Display                   | Thread-safe C libra<br>The following table show<br>Table 1. Functions that are | s the C library functions that are thread-safe. ■                                                                                                                                                                                                                                                                                                |

| Select topic: Found: 4                                                                                                                          | Functions                                                                      | Description                                                                                                                                                                                                                                                                                                                                      |

| Cand C++ Libraries Cand C++ 1<br>Libraries and Roatin Libraries a 2<br>Libraries and Roatin Libraries a 3<br>Libraries and Roatin Libraries a 4 | <pre>calloc(), free(),</pre>                                                   | The heap functions are thread-<br>safe if the <u>mutex</u> * functions are<br>implemented.                                                                                                                                                                                                                                                       |

|                                                                                                                                                 | <pre>malloc(),</pre>                                                           | A single heap is shared between<br>all threads, and mutexes are<br>used to avoid data corruption                                                                                                                                                                                                                                                 |

|                                                                                                                                                 | realloc()                                                                      | when there is concurrent access.<br>Each heap implementation is<br>responsible for doing its own<br>locking. If you supply your own<br>allocator, it must also do its own<br>locking. This enables it to do fine-<br>grained locking if required, rather<br>than protecting the entire heap<br>with a single mutex (coarse-<br>grained locking). |

| <ul> <li>☐ Search previous results</li> <li>☑ Match similar words</li> <li>☐ Search titles only</li> </ul>                                      | alloca()                                                                       | alloca() is thread-safe because it allocates memory on the stack.                                                                                                                                                                                                                                                                                |

| - Sedjor tutes only                                                                                                                             |                                                                                |                                                                                                                                                                                                                                                                                                                                                  |

Figure 2-2 Run-time Library Configuration

### 2.1 OS\_STACK\_SIZE / OS\_HEAP\_SIZE Set-up

The file  $Abassi_CORTEXM4_KEIL.s$  contains the start-up code for "C" applications built with the Keil  $\mu$ Vision4 for the ARM that use the Abassi RTOS. There should be no other start-up file included in the project.

There are two definitions that are used to set-up the heap size (memory used by malloc()) and the stack size for the function main(), which is the highest priority task at start-up (known in Abassi as Adam&Eve). These definitions are located at around line 30 in the Abassi\_CORTEXM4\_KEIL.s file and are shown in the following table:

#### Table 2-1 OS\_STACK\_SIZE and OS\_HEAP\_SIZE

```

IF (:DEF: OS_HEAP_SIZE) == {FALSE}

OS_HEAP_SIZE EQU 4096 ; Heap size (malloc()) in bytes / Set-up to your needs

ENDIF

IF (:DEF: OS_STACK_SIZE) == {FALSE}

OS_STACK_SIZE EQU 1024 ; A&E stack size in bytes / Set-up to your needs

ENDIF

```

A heap size of 4096 bytes and a stack size of 1024 bytes are the values set in the distribution code; modify these values according to the needs of the application.

Alternatively, it is possible to overload the values of <code>OS\_HEAP\_SIZE</code> and <code>OS\_STACK\_SIZE</code> set in <code>Abassi\_CORTEXM4\_KEIL.s</code> by using the assembler command line option <code>-predefine</code> and specifying the desired heap size and stack size as shown in the following example, where the heap size is set to 2048 bytes, and the stack size is set to 512 bytes:

#### Table 2-2 Command line set of Heap and Stack sizes

```

armasm ... -predefine "OS_HEAP_SIZE SETA 2048" -predefine "OS_STACK_SIZE SETA 512" ...

```

The heap and stack sizes can also be set through the GUI, in the "Asm" menu, as shown in the following figure:

| 🕅 Options for Target 'Target 1'                                                             |

|---------------------------------------------------------------------------------------------|

| Device Target Output Listing User C/C++ Asm Linker Debug Utilities                          |

| Conditional Assembly Control Symbols                                                        |

| Define: OS_HEAP_SIZE=2048 OS_STACK_SIZE=512                                                 |

| Undefine:                                                                                   |

| Language / Code Generation                                                                  |

| Split Load and Store Multiple                                                               |

| Read-Only Position Independent                                                              |

| Read-Write Position Independent                                                             |

| Thumb Mode                                                                                  |

|                                                                                             |

| No W <u>a</u> mings                                                                         |

| Include                                                                                     |

| Paths                                                                                       |

| Misc                                                                                        |

| Controls                                                                                    |

| Assembler \ARM\CMSIS\Include -I C:\Keil\ARM\Inc\ST\STM32F4xxpd "OS_HEAP_SIZE SETA 2048"pd 🔺 |

| control "OS_STACK_SIZE SETA 512" -list "*.lst" -xref -o "*.o" -depend "*.d"                 |

| sung                                                                                        |

|                                                                                             |

| OK Cancel Defaults Help                                                                     |

Figure 2-3 GUI set of Heap and Stack sizes

#### 2.2 Interrupt Stack Set-up

It is possible, and is highly recommended, to use a hybrid stack when nested interrupts occur in an application. Using this hybrid stack, specially dedicated to the interrupts, removes the need to allocate extra room to the stack of every task in the application to handle the interrupt nesting. This feature is controlled by the value set by the definition OS\_ISR\_STACK, located around line 35 in the file Abassi\_CORTEXM4\_KEIL.s. To disable this feature, set the definition of OS\_ISR\_STACK to a value of zero. To enable it, and specify the interrupt stack size, set the definition of OS\_ISR\_STACK to the desired size in bytes (see Section 4 for information on stack sizing). As supplied in the distribution, the hybrid stack feature is enabled and a size of 1024 bytes is allocated; this is shown in the following table:

Table 2-3 OS ISR STACK

```

IF (:DEF: OS_ISR_STACK) == {FALSE}

OS_ISR_STACK EQU 1024 ; If using a dedicated stack for the nested ISRs

ENDIF ; 0 if not used, otherwise size of stack in bytes

```

Alternatively, it is possible to overload the OS\_ISR\_STACK value set in Abassi\_CORTEXM4\_KEIL.s by using the assembler command line option -D and specifying the desired hybrid stack size as shown in the following example, where the hybrid stack size is set to 512 bytes:

Table 2-4 Command line set of OS ISR STACK

```

armasm ... -predefine "OS_ISR_STACK SETA 512" ...

```

The hybrid stack size can also be set through the GUI, in the "Asm" menu, as shown in the following figure:

| V Options for Target 'Target 1'                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Target Output Listing User C/C++ Asm Linker Debug Utilities                                                                                                                                            |

| Conditional Assembly Control Symbols                                                                                                                                                                          |

| Define: OS_ISR_STACK=512                                                                                                                                                                                      |

| Undefine:                                                                                                                                                                                                     |

| Language / Code Generation                                                                                                                                                                                    |

| Split Load and Store Multiple                                                                                                                                                                                 |

| Read-Only Position Independent                                                                                                                                                                                |

| Read-Write Position Independent                                                                                                                                                                               |

| Thumb Mode                                                                                                                                                                                                    |

| No Warnings                                                                                                                                                                                                   |

|                                                                                                                                                                                                               |

| Include                                                                                                                                                                                                       |

| Paths                                                                                                                                                                                                         |

| Misc                                                                                                                                                                                                          |

|                                                                                                                                                                                                               |

| Assembler -cpu Cortex-M4.fp -pd "EVAL SETA 1" -g -apcs=interwork -I C:\Keil\ARM\RV31\lnc -I C:\Keil<br>control \ARM\CMSIS\Include -I C:\Keil\ARM\Inc\ST\STM32F4xx -pd "OS_ISR_STACK SETA 512" -list<br>string |

|                                                                                                                                                                                                               |

| OK Cancel Defaults Help                                                                                                                                                                                       |

Figure 2-4 GUI set of OS\_ISR\_STACK

### 2.3 Saturation Bit Set-up

In the ARM Cortex-M4 status register, there is a sticky bit to indicate if an arithmetic saturation or overflow has occurred during a DSP instruction; this is the Q flag in the status register (bit #27). By default, this bit is not kept localized at the task level, as it needs extra processing during a context switch to do so; instead, it is propagated across all tasks. This choice was made because most applications do not care about the value of this bit.

If this bit is relevant for an application, even in a single task, then it must be kept locally in each task. To keep the meaning of the saturation bit localized, the token OS\_HANDLE\_PSR\_Q must be set to a non-zero value; to disable it, it must be set to a zero value. This is located at around line 45 in the file Abassi\_CORTEXM4\_KEIL.s. The distribution code disables the localization of the Q bit, setting the token OS\_HANDLE\_PSR\_Q to zero, as shown in the following table:

#### **Table 2-5 Saturation Bit configuration**

```

IF (:DEF: OS_HANDLE_PSR_Q) == {FALSE}

OS_HANDLE_PSR_Q EQU 0 ; If we keep the Q bit (saturation) on per tasks

ENDIF

```

Alternatively, it is possible to overload the OS\_HANDLE\_PSR\_Q value set in Abassi\_CORTEXM4\_KEIL.s by using the assembler command line option -D and specifying the desired setting with the following:

Table 2-6 Command line set of Saturation Bit configuration

```

armasm ... -predefine "OS_HANDLE_PSR_Q SETA 1" ...

```

The saturation bit configuration can also be set through the GUI, in the "Asm" menu, as shown in the following figure:

| 🕅 Options for Target 'Target 1'                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device   Target   Output   Listing   User   C/C++ Asm   Linker   Debug   Utilities                                                                                                                           |

| Conditional Assembly Control Symbols                                                                                                                                                                         |

| Define: OS_HANDLE_PSR_Q                                                                                                                                                                                      |

| Undefine:                                                                                                                                                                                                    |

| Language / Code Generation                                                                                                                                                                                   |

| Split Load and Store Multiple                                                                                                                                                                                |

| Read-Only Position Independent     Read-Write Position Independent                                                                                                                                           |

| Thumb Mode                                                                                                                                                                                                   |

| — — — — — — — — — — — — — — — — — — —                                                                                                                                                                        |

|                                                                                                                                                                                                              |

| Paths                                                                                                                                                                                                        |

| Misc<br>Controls                                                                                                                                                                                             |

| Assembler -cpu Cortex-M4.fp -pd "EVAL SETA 1" -gapcs=interwork -1 C:\Keil\ARM\RV31\Inc -I C:\Keil \ARM\RV31\Inc -I C:\Keil \ARM\CMSIS\Include -I C:\Keil\ARM\Inc\ST\STM32F4xx -pd "OS_HANDLE_PSR_Q SETA 1" * |

|                                                                                                                                                                                                              |

| OK Cancel Defaults Help                                                                                                                                                                                      |

Figure 2-5 GUI set of Saturation Bit configuration

### 2.4 FPU set-up

The assembly file Abassi\_CORTEXM4\_KEL.s, depending on its configuration, handle three different types of FPU use. They are:

- > The FPU is always disable

- > The FPU is always enable

- > The FPU is turned on and turned off during runtime

The file Abassi\_CORTEXM4\_KEIL.s is aware of the enabling of disabling of FPU by the compiler through the use of the KEIL build definition {CPU}, automatically defined when the assembler is set-up to enable the FPU instructions; {CPU} is then defined as Cortex-M4.fp. There are two ways to set-up the assembler to support the FPU instruction. This is done on the command line with the option --cpu:

#### Table 2-7 Command line enabling of the FPU

| armasm | <br>cpu      | CortexM4.fp |  |

|--------|--------------|-------------|--|

|        | - <u>1</u> - |             |  |

The enabling of the FPU can also be performed through the GUI, in the *Target* menu, by setting the Floating Point Hardware to a value different than *Not Used*.

| 🔣 Options for Target 'Target 1' |                              |         |              |            |                  |              | ×      |

|---------------------------------|------------------------------|---------|--------------|------------|------------------|--------------|--------|

| Device Target Output Listing    | User C/C++                   | Asm     | Linker       | Debug      | Jtilities        |              |        |

| STMicroelectronics STM32F407Z   | G<br><u>X</u> tal (MHz): 25. | 0       | -Code 0      | ieneration | I                |              |        |

| Operating system: None          |                              | •       |              |            | Module Optimizat |              |        |

| System-Viewer File (.Sfr):      |                              |         | U            | se MicroL  |                  | 🗌 Big Endian |        |

| SFD\ST\STM32F4xx\STM32F4        | ox.sfr                       |         | Floati       | ng Point H | lardware:        | Use FPU      |        |

| 1                               |                              |         |              |            |                  |              |        |

| Read/Only Memory Areas          |                              |         | Read/        | Write Men  | nory Areas       |              |        |

| default off-chip Start          | Size                         | Startup | default      | off-chip   | Start            | Size         | Nolnit |

| ROM1:                           |                              | 0       |              | RAM1:      |                  |              |        |

| ROM2:                           |                              | 0       |              | RAM2:      |                  |              |        |

| ROM3:                           |                              | 0       |              | RAM3:      |                  |              |        |

| on-chip                         |                              |         |              | on-chip    |                  |              |        |

| IROM1: 0x8000000                | 0x100000                     | œ       | $\checkmark$ | IRAM1:     | 0x20000000       | 0x20000      |        |

| IROM2:                          |                              | 0       |              | IRAM2:     | 0x10000000       | 0x10000      |        |

| ,                               | ,                            |         |              |            | ,                |              |        |

|                                 | ОК                           | Can     | cel          | Defa       | ults             |              | Help   |

#### Figure 2-6 GUI enabling of the FPU

When the FPU is enabled, each task can use a different configuration of the FPU (through the FPCSR register), as the contents of this register is part of the task context save. All tasks upon start will have their local FPCSR value set according to the value of FPCSR register upon calling OSstart(). This means if the application globally requires a different setting of the FPU than the default set by the compiler, the FPCSR must be modified before calling OSstart().

It is also possible to turn on and turn off the FPU during runtime, and the ON / OFF setting is also kept on a per task basis. This means the FPU can be enable in a set of tasks when it is not for the other tasks in the application. All tasks, upon start, will inherit the same ON / OFF state of the FPU as when <code>OSstart()</code> was called. When this feature is required, the build option <code>OS\_FPU\_ON\_OFF</code> definition, located around line 50 in the file <code>Abassi\_CORTEXM4\_KEIL.s</code>, must be set to a non-zero value. The distribution code does not enable the capability of turning the FPU ON and OFF during runtime, setting the token <code>OS\_FPU\_ON\_OFF</code> to zero, as shown in the following table:

#### Table 2-8 FPU run time ON / OFF configuration

```

IF (:DEF: OS_FPU_ON_OFF) == {FALSE}

OS_FPU_ON_OFF EQU 0 ; If the FPU can be turned ON/OFF during runtime

ENDIF

```

Alternatively, it is possible to overload the OS\_FPU\_ON\_OFF value set in Abassi\_CORTEXM4\_KEIL.s by using the assembler command line option -D and specifying the desired setting with the following:

Table 2-9 Command line set of OS\_FPU\_ON\_OFF

```

armasm ... -predefine "OS_FPU_ON_OFF SETA 1" ...

```

The indication the FPU is turned on and off during runtime can also be set through the GUI, in the "*Asm*" menu, as shown in the following figure:

| 🕅 Options for Target 'Target 1'                                                                | x |

|------------------------------------------------------------------------------------------------|---|

| Device Target Output Listing User C/C++ Asm Linker Debug Utilities                             |   |

| Conditional Assembly Control Symbols                                                           |   |

| Define: OS_FPU_ON_OFF                                                                          |   |

| Undefine:                                                                                      |   |

| Language / Code Generation                                                                     |   |

| ☐ Split Load and Store Multiple                                                                |   |

| Read-Only Position Independent                                                                 |   |

| Read-Write Position Independent                                                                |   |

| Thumb Mode                                                                                     |   |

|                                                                                                |   |

| No Wamings                                                                                     |   |

|                                                                                                | - |

| Include<br>Paths                                                                               |   |

| Misc                                                                                           |   |

| Controls                                                                                       |   |

| Assembler  cpu Cortex-M4pd "EVAL SETA 1" -gapcs=interwork -I C:\Keil\ARM\RV31\lnc -I C:\Keil 🔺 |   |

| control \ARM\CMSIS\Include -I C:\Keil\ARM\Inc\ST\STM32F4xx -pd "OS_FPU_ON_OFF SETA 1" -list    |   |

| string                                                                                         |   |

|                                                                                                |   |

| OK Cancel Defaults Help                                                                        |   |

|                                                                                                |   |

Figure 2-7 GUI set of OS\_FPU\_ON\_OFF

There are a two requirements to fulfill when the FPU is turned on and off during runtime. The first one, which is not related to the RTOS, but is a restriction by the Cortex core, is to never have a different enable setting of the FPU between the entry and the exit of an ISR. This means that turning ON and then OFF the FPU in an interrupt is safe. But turning it ON, without turning it OFF before exiting the interrupt, will crash the application. If the FPU is ON upon entry in the interrupt and it gets turned OFF in the interrupt without being turned back ON will trigger an access fault exception.

The second requirement when the FPU is turned ON and OFF during runtime is that it is necessary to set the SVCall (Service call exception vector #11, interrupt #-5) priority to the highest level. This is configured in the System Handler Priority Register 2 (SHPR2) register. If this register is not modified, then at start-up the priority of the SVCall exception is set to the higher level.

NOTE: When the FPU is turned OFF in a task, the setting of the FPCSR will quite likely to be set back to the task start-up value upon turning ON the FPU afterward.

### 3 Interrupts

The Abassi RTOS needs to be aware when kernel requests are performed inside or outside an interrupt context. For all interrupt sources (except interrupt numbers less than -1) the Abassi RTOS provides an interrupt dispatcher, which allows it to be interrupt-aware. This dispatcher achieves two goals. First, the kernel uses it to know if a request occurs within an interrupt context or not. Second, using this dispatcher reduces the code size, as all interrupts share the same code for the decision making of entering the kernel or not at the end of the interrupt: there is no need to add a preamble / epilogue in the functions handling the interrupts.

The distribution makes provision for 241 sources of interrupts, as specified by the token OS\_N\_INTERRUPTS in the file Abassi\_CORTEXM4\_KEIL.s, and the internal default value used by Abassi.c. Even though the Nested Vectored Interrupt Controller (NVIC) peripheral supports a maximum of 256 interrupts on the Cortex-M4, the first 15 entries of the interrupt vector table are hard mapped to dedicated handlers (the interrupt number -1, which is attached to SysTick, is not hard mapped but is handled by the ISR dispatcher).

### 3.1 Interrupt Handling

### 3.1.1 Interrupt Table Size

Most devices do not require all 256 interrupts, as they typically only handle between 64 and 128 sources of interrupts. The interrupt table can be easily reduced to recover code space, and at the same time recover the same amount of data memory. There are two files affected: in Abassi\_CORTEXM4\_KEIL.s, the ARM interrupt table itself must be shrunk, and the value used in the file Abassi.c, in order to reduce the ISR dispatcher table look-up. The interrupt table size is defined by the token OS\_N\_INTERRUPTS in the file Abassi\_CORTEXM4\_KEIL.s around line 35. For the value used by Abassi.c, the default value can be overloaded by defining the token OS\_N\_INTERRUPTS when compiling Abassi.c. The distribution table size is set to 241; that is the NVIC maximum of 256 minus the 15 hard mapped exceptions.

For example, the STM32F407 device from ST Microelectronics uses only the first 100 entries of the interrupt table (84 external interrupts plus the standard 16 exceptions). The 256 entries table can therefore be reduced to 100. The value to set in Abassi\_CortexM4\_ISR.s files is 85, which is the total of 100 entries minus 15 (there are 15 hard mapped exceptions). The changes are shown in the following table:

#### Table 3-1 Abassi\_CortexM4\_KEIL.s interrupt table sizing

```

...

IF (:DEF: OS_N_INTERRUPTS) == {FALSE} ; # of entries in the interupt table mapped to

OS_N_INTERUPTS EQU 85 ; ISRdispatch()

ENDIF

...

```

Alternatively, it is possible to overload the OS\_N\_INTERRUPTS value set in Abassi\_CORTEXM4\_KEIL.s by using the assembler command line option -D and specifying the desired setting with the following:

#### Table 3-2 Command line set the interrupt table size

```

armasm ... -predefine "OS_N_INTERRUPTS SETA 85" ...

```

The overloading of the default interrupt vector look-up table used by Abassi.c is done by using the compiler command line option -D and specifying the desired setting with the following:

Table 3-3 Overloading the interrupt table sizing for Abassi.c

```

armcc ... -DOS_N_INTERRUPTS=85 ...

```

The interrupt table size used by Abassi\_CORTEXM4\_KEIL.s can also be set through the GUI, in the "Asm" menu, as shown in the following figure:

| 👿 Options for Target 'Target 1'                                                          | ×    |

|------------------------------------------------------------------------------------------|------|

| Device Target Output Listing User C/C++ Asm Linker Debug Utilities                       |      |

| Conditional Assembly Control Symbols                                                     |      |

| Define: OS_N_INTERRUPTS=85                                                               |      |

| U <u>n</u> define:                                                                       |      |

| Language / Code Generation                                                               | _    |

| Split Load and Store Multiple                                                            |      |

| Read-Only Position Independent                                                           |      |

| Read-Write Position Independent                                                          |      |

| Thumb Mode                                                                               |      |

|                                                                                          |      |

| No Wamings                                                                               |      |

| Include                                                                                  |      |

| Paths                                                                                    | ···  |

| Misc                                                                                     | - 11 |

| Controls                                                                                 | _    |

| Assembler                                                                                |      |

| control \ARM\CMSIS\Include -I C:\Keil\ARM\Inc\ST\STM32F4xx -pd "OS_N_INTERRUPTS SETA 85" | _    |

| string                                                                                   | Ť    |

|                                                                                          |      |

| OK Cancel Defaults H                                                                     | lelp |

Figure 3-1 GUI set of os\_n\_interrupts

The interrupt table look-up size used by Abassi.c can also be overloaded through the GUI, in the "C/C++" menu, as shown in the following figure:

| V Options for Target 'Target 1'                                                                                                                                                     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device   Target   Output   Listing   User   C/C++   Asm   Linker   Debug   Utilities                                                                                                |  |

| Preprocessor Symbols                                                                                                                                                                |  |

| Define: OS_N_INTERRUPTS=85                                                                                                                                                          |  |

| Undefine:                                                                                                                                                                           |  |

| Language / Code Generation                                                                                                                                                          |  |

| Strict ANSI C Warnings:                                                                                                                                                             |  |

| Optimization: Level 0 (-00) ▼ Enum Container always int <ul> <li>(unspecified&gt; ▼</li> </ul>                                                                                      |  |

| Optimize for Time     Plain Char is Signed                                                                                                                                          |  |

| Split Load and Store Multiple Read-Only Position Independent                                                                                                                        |  |

| One <u>E</u> LF Section per Function <u>R</u> ead-Write Position Independent                                                                                                        |  |

| Include                                                                                                                                                                             |  |

| Paths J                                                                                                                                                                             |  |

| Controls                                                                                                                                                                            |  |

| Compiler c-cpu Cottex-M4 fp -D_EVAL-g -O0 -apcs=interwork -I C:\Keil\ARM\RV31\lnc-I C:\Keil\ARM<br>\CMSIS\lnclude -I C:\Keil\ARM\lnc\ST\STM32F4xx -DOS_N_INTERRUPTS="85" -o "*.o" - |  |

| OK Cancel Defaults Help                                                                                                                                                             |  |

Figure 3-2 GUI set of os\_n\_interrupts

### 3.1.2 Interrupt Installer

Attaching a function to a regular interrupt is quite straightforward. All there is to do is use the RTOS component <code>OSisrInstall()</code> to specify the interrupt number and the function to be attached to that interrupt number. For example, Table 3-4 shows the code required to attach the <code>SysTick</code> interrupt to the RTOS timer tick handler (<code>TIMtick</code>):

#### Table 3-4 Attaching a Function to an Interrupt

```

#include "Abassi.h"

...

OSstart();

...

OSisrInstall(-1, &TIMtick);

/* Set-up the count reload and enable SysTick interrupt */

... /* More ISR setup */

OSeint(1); /* Global enable of all interrupts */

```

NOTE: OSisrInstall() uses the interrupt number, NOT the interrupt vector number.

At start-up, once <code>OSstart()</code> has been called, all <code>OS\_N\_INTERRUPTS</code> interrupt handler functions are set to a "do nothing" function, named <code>OSinvalidISR()</code>. If an interrupt function is attached to an interrupt number using the <code>OSisrInstall()</code> component <u>before</u> calling <code>OSstart()</code>, this attachment will be removed by <code>OSstart()</code>, so <code>OSisrInstall()</code> should never be used before <code>OSstart()</code> has ran. When an interrupt handler is removed, it is very important and necessary to first disable the interrupt source, then the handling function can be set back to <code>OSinvalidISR()</code>. This is shown in Table 3-5:

#### Table 3-5 Invalidating an ISR handler

```

#include "Abassi.h"

...

/* Disable the interrupt source */

OSisrInstall(Number, &OSinvalidISR);

...

```

When an application needs to disable / enable the interrupts, the RTOS supplied functions <code>OSdint()</code> and <code>OSeint()</code> should be used.

The Nested Vectored Interrupt Controller (NVIC) on the Cortex-M4 does not clear the interrupt generated by a peripheral; neither does the RTOS. If the generated interrupt is a pulse (as for the SysTick interrupt), there is nothing to do to clear the interrupt request. However, if the generated interrupt is a level interrupt, the peripheral generating the interrupt must be informed to remove the interrupt request. This operation must be performed in the interrupt handler otherwise the interrupt will be re-entered over and over.

### 3.2 Interrupt Priority and Enabling

To properly configure interrupts, the interrupt priority must be set, and the peripheral configured to generate interrupts and enable them. There is no software provided to perform these operations, as this functionality is already available. First, Keil  $\mu$ Vision4 supports the Cortex Microcontroller Software Interface Standard (CMSIS), which provides everything required to program the processor peripherals. Second, most chip manufacturers provide code to configure the specifics on their devices.

### 3.3 Fast Interrupts

Fast interrupts are supported on this port. A fast interrupt is an interrupt that never uses any component from Abassi, and as the name says, is desired to operate as fast as possible. To set-up a fast interrupt, all there is to do is to set the address of the interrupt function in the corresponding entry in the interrupt vector table used by the Cortex-M4 processor. The area of the interrupt vector table to modify is located in the file Abassi CORTEXM4 KEIL.s around line 100.

For example, on a ST Microelectronics STM32F407 device, UART #1 is attached to interrupt number 37 (interrupt vector number 53) and the UART #2 is attached to the interrupt number 38 (interrupt vector number 54). The code to modify is located in the macro loop that initializes the interrupt table that sets the ISR dispatcher as the default interrupt handler. All there is to do is add checks on the token holding the interrupt number, such that, when the interrupt number value matches the desired interrupt number, the appropriate address gets inserted in the table instead of the address of ISRdispatch(). The original macro loop code and modified one are shown in the following two tables:

#### Table 3-6 Distribution interrupt table code

```

GBLA INT_NMB ; Interrupt number in the loop

INT_NMB SETA -1 ; Can't use < as < is unsigned

WHILE INT_NMB != (OS_N_INTERRUPTS-1); Map all external interrupts to ISRdispatch()

DCD ISRdispatch

INT_NMB SETA INT_NMB+1

WEND

```

Attaching a fast interrupt handler to the UART #1 and another one to UART#2, assuming the names of the interrupt functions to attach are respectively UART1\_IRQhandler() and UART2\_IRQhandler() is shown in Table 3-7:

#### Table 3-7 STM32F407 UART 1 / 2 Fast Interrupts

```

EXTERN USART1 IRQhandler

EXTERN USART2 IRQhandler

GBLA INT NMB

; Interrupt number in the loop

INT NMB SETA -1

; Can't use < as < is unsigned

WHILE INT NMB != (OS N INTERRUPTS-1); Map all external interrupts to ISRdispatch()

IF INT NMB == 37

; When is interrupt # 37, set UART #1 handler

UART1 IRQhandler

DCD

ELSEIF INT NMB == 38

; When is interrupt # 38, set UART #2 handler

DC32 UART2 IRQhandler

ELSE

; All others interrupt # set to ISRdispatch()

DCD

ISRdispatch

ENDIF

INT NMB SETA INT NMB+1

WEND

...

```

It is important to add the EXTERN statement, otherwise there will be an error during the assembly of the file. NOTE: If an Abassi component is used inside a fast interrupt, the application will misbehave. Even if the hybrid interrupt stack feature is enabled (see Section 0), fast interrupts will not use that stack. This translates into the need to reserve room on all task stacks for the possible nesting of fast interrupts. To make the fast interrupts also use a hybrid interrupt stack, a prologue and epilogue must be used around the call to the interrupt handler. The prologue and epilogue code to add is almost identical to what is done in the regular interrupt dispatcher. Reusing the example of the UART #1 on the STM32F407 device, this would look something like:

**Table 3-8 Fast Interrupt with Dedicated Stack**

```

...

ELSEIF INT NMB == 37

DC32 UART1_preHandler

; Set the addres of the pre handler

; in the interrupt table

•••

...

THUMB

ALIGN

AREA

|.text|, CODE, READONLY

EXTERN UART1 IRQhandler

UART1 preHandler

cpsid I

; Disable ISR to protect against nesting

mov

r0, sp

; Memo current stack pointer

ldr

sp, =UART1_stack

; Stack dedicated to this fast interrupt

I

; The stack is now hybrid, nesting safe

cpsie

push

{r0, lr}

; Preserve original sp & EXC RETURN

bl

UART1 IRQhandler

; Enter the interrupt handler

{r0, lr}

; Recover original sp & EXC RETURN

pop

; Recover pre-isr stack

mov

sp, r0

bx

lr

; Exit from the interrupt

...

ALIGN

AREA

HEAP, NOINIT, READWRITE, ALIGN=3

; Room for the fast interrupt stack

SPACE

UART1 stack size

UART1 stack

...

```

The same code, with unique labels, must be repeated for each of the fast interrupts.

### 3.4 Nested Interrupts

The interrupt controller allows nesting of interrupts; this means an interrupt of higher priority will interrupt the processing of an interrupt of lower priority. Individual interrupt sources can be set to one of 8 levels, where level 0 is the highest and 7 is the lowest. This implies that the RTOS build option OS\_NESTED\_INTS must be set to a non-zero value. The exception to this is an application where all enabled interrupts handled by the RTOS ISR dispatcher are set, without exception, to the same priority; then interrupt nesting will not occur. In that case, and only that case, can the build option OS\_NESTED\_INTS be set to zero. As this latter case is quite unlikely, the build option OS\_NESTED\_INTS is always overloaded when compiling the RTOS for the ARM Cortex-M4. If the latter condition is guaranteed, the overloading located after the pre-processor directive can be modified. The code affected in Abassi.h is shown in Table 3-9 below and the line to modify is the one with #define OX NESTED INTS 1:

#### Table 3-9 Removing interrupt nesting

```

#elif defined(__CC_ARM)

#define OX NESTED INTS 0 /* The ARM has 8 nested (NIVC) interrupt levels */

```

Or if the build option OS\_NESTED\_INTS is desired to be propagated:

#### Table 3-10 Propagating interrupt nesting

```

#elif defined(__CC_ARM)

#define OX_NESTED_INTS OS_NESTED_INTS

```

The Abassi RTOS kernel never disables interrupts, but there is a few very small regions within the interrupt dispatcher where interrupts are temporarily disabled due to the nesting (a total of between 10 to 20 instructions).

The kernel is never entered as long as interrupt nesting exists. In all interrupt functions, when a RTOS component that needs to access some kernel functionality is used, the request(s) is/are put in a queue. Only once the interrupt nesting is over (i.e. when only a single interrupt context remains) is the kernel entered at the end of the interrupt, when the queue contains one or more requests, and when the kernel is not already active. This means that only the interrupt handler function operates in an interrupt context, and only the time the interrupt function is using the CPU are other interrupts of equal or lower level blocked by the interrupt controller.

### 4 Stack Usage

The RTOS uses the tasks' stack for two purposes. When a task is blocked or ready to run but not running, the stack holds the register context that was preserved when the task got blocked or preempted. Also, when an interrupt occurs, the register context of the running task must be preserved in order for the operations performed during the interrupt to not corrupt the contents of the registers used by the task when it got interrupted. For the Cortex-M4, the context save contents of a blocked or pre-empted task is different from the one used in an interrupt, and is also different if the compiler is set to use the FPU or not. The following table lists the number of bytes required by each type of context save operation:

| Description                                                     | <b>Context save</b> |

|-----------------------------------------------------------------|---------------------|

| Blocked/Preempted task context save (FPU OFF)                   | 40 bytes            |

| Interrupt dispatcher context save (OS_ISR_STACK == 0) (FPU OFF) | 40 bytes            |

| Interrupt dispatcher context save (OS_ISR_STACK != 0) (FPU OFF) | 48 bytes            |

| Blocked/Preempted task context save (FPU ON)                    | 112 bytes           |

| Interrupt dispatcher context save (OS_ISR_STACK == 0) (FPU ON)  | 120 bytes           |

| Interrupt dispatcher context save (OS_ISR_STACK != 0) (FPU ON)  | 128 bytes           |

#### **Table 4-1 Context Save Stack Requirements**

The numbers for the interrupt dispatcher context save include the 32 bytes (FPU OFF) or the 96 bytes (FPU ON) the processor pushes on the stack when it enters the interrupt servicing.

When sizing the stack to allocate to a task, there are three factors to take in account. The first factor is simply that every task in the application needs at least the area to preserve the task context when it is preempted or blocked. Second, one must take into account how many levels of nested interrupts exist in the application. As a worst case, all levels of interrupts may occur and becoming fully nested. So if N levels of interrupts are used in the application, provision should be made to hold N times the size of an ISR context save on each task stack, plus any added stack used by all the interrupt handler functions. Finally, add to all this the stack required by the code implementing the task operation.

NOTE: The ARM Cortex M4 processor needs alignment on 8 bytes for some instructions accessing memory. When stack memory is allocated, Abassi guarantees the alignment. This said, when sizing OS\_STATIC\_STACK or OS\_ALLOC\_SIZE, make sure to take in account that all allocation performed through these memory pools are by block size multiple of 8 bytes.

If the hybrid interrupt stack (see Section 0) is enabled, then the above description changes: it is only necessary to reserve room on task stacks for a single interrupt context save (this excludes the interrupt function handler stack requirements) and not the worst-case nesting. With the hybrid stack enabled, the second, third, and so on interrupts use the stack dedicated to the interrupts. The hybrid stack is enabled when the OS\_ISR\_STACK token in the file Abassi\_CORTEXM4\_KEIL.s is set to a non-zero value (see Section 2.2).

### 5 Search Set-up

The Abassi RTOS build option OS\_SEARCH\_FAST offers three different algorithms to quickly determine the next running task upon task blocking. The following table shows the measurements obtained for the number of CPU cycles required when a task at priority 0 is blocked, and the next running task is at the specified priority. The number of cycles includes everything, not just the search cycle count. The number of cycles was measured using the SysTick peripheral, which decrements the counter once every CPU cycle. The second column is when OS\_SEARCH\_FAST is set to zero, meaning a simple array traversing. The third column, labeled Look-up, is when OS\_SEARCH\_FAST is set to 1, which uses an 8 bit look-up table. Finally, the last column is when OS\_SEARCH\_FAST is set to 5 (Keil/Cortex-M4 int are 32 bits, so 2^5), meaning a 32 bit look-up table, further searched through successive approximation. The compiler optimization for this measurement was set to Level High / Speed optimization. The RTOS build options were set to the minimum feature set, except for option OS\_PRIO\_CHANGE set to non-zero. The presence of this extra feature provokes a small mismatch between the result for a difference of priority of 1, with OS\_SEARCH\_FAST set to zero, and the latency results in Section 7.2.

When the build option OS\_SEARCH\_ALGO is set to a negative value, indicating to use a 2-dimensional linked list search technique instead of the search array, the number of CPU cycles is constant at 244 cycles.

| Priority | Linear search | Look-up | Approximation |

|----------|---------------|---------|---------------|

| 1        | 247           | 276     | 309           |

| 2        | 254           | 283     | 309           |

| 3        | 261           | 290     | 309           |

| 4        | 268           | 297     | 309           |

| 5        | 275           | 304     | 309           |

| 6        | 282           | 311     | 309           |

| 7        | 289           | 318     | 309           |

| 8        | 296           | 280     | 309           |

| 9        | 303           | 284     | 309           |

| 10       | 310           | 291     | 309           |

| 11       | 317           | 298     | 309           |

| 12       | 324           | 305     | 309           |

| 13       | 331           | 312     | 309           |

| 14       | 338           | 319     | 309           |

| 15       | 345           | 326     | 309           |

| 16       | 352           | 288     | 309           |

| 17       | 359           | 292     | 309           |

| 18       | 366           | 299     | 309           |

| 19       | 373           | 306     | 309           |

| 20       | 380           | 313     | 309           |

| 21       | 387           | 320     | 309           |

| 22       | 394           | 327     | 309           |

| 23       | 401           | 334     | 309           |

| 24       | 408           | 296     | 309           |

#### Table 5-1 Search Algorithm Cycle Count

When OS\_SEARCH\_FAST is set to 0, each extra priority level to traverse requires exactly 7 CPU cycles. When OS\_SEARCH\_FAST is set to 1, each extra priority level to traverse requires exactly 7 CPU cycles, except when the priority level is an exact multiple of 8; then there is a sharp reduction of CPU usage. Overall, setting OS\_SEARCH\_FAST to 1 adds 27 cycles of CPU for the search compared to setting OS\_SEARCH\_FAST to zero. But when the next ready to run priority is less than 8, 16, 24, ... then there is an extra 8 cycles needed, but without the 8 times 8 cycle accumulation. Finally, the third option, when OS\_SEARCH\_FAST is set to 5, delivers a perfectly constant CPU usage, as the algorithm utilizes a successive approximation search technique (when the delta is 32 or more, the CPU cycle count is 317, for 64 or more, it is 325).

The first observation, when looking at this table, is that the second option, when OS\_SEARCH\_FAST is set to 1, is either less CPU efficient than the first option, the one when OS\_SEARCH\_FAST is set to 0, or less efficient than the third option OS\_SEARCH\_FAST is set to 5. So, the build option OS\_SEARCH\_FAST should never be set to 1, as it is the least efficient method. The other observation is that the first option (OS\_SEARCH\_FAST set to 0) delivers better CPU performance than the third option (OS\_SEARCH\_FAST set to 5) when the search spans less than 7 to 8 priority levels. So, if an application has tasks spanning less than 7 to 8 priority levels, the build option OS\_SEARCH\_FAST should be set to 0; for all other cases, the build option OS\_SEARCH\_FAST should be set to 5.

Setting the build option OS\_SEARCH\_ALGO to a non-negative value minimizes the time needed to change the state of a task from blocked to ready to run, and not the time needed to find the next running task upon blocking/suspending of the running task. If the application needs are such that the critical real-time requirement is to get the next running task up and running as fast as possible, then set the build option OS\_SEARCH\_ALGO to a negative value.

### 6 Chip Support

No chip support is provided with the distribution code because Keil  $\mu$ Vision4 for the ARM supports the Cortex Microcontroller Software Interface Standard (CMSIS). Therefore, all peripherals on the Cortex-M4 can be accessed through the CMSIS. Also, most device manufacturers provide code to configure the peripherals on their devices.

### 7 Measurements

This section gives an overview of the memory requirements and the CPU latency encountered when the RTOS is used on the ARM Cortex-M4 and compiled with Keil  $\mu$ Vision4. The CPU cycles are exactly the CPU clock cycles, as the processor typically executes one instruction at every clock transition.

### 7.1 Memory

The memory numbers are supplied for the two limit cases of build options (and some in-between): the smallest footprint is the RTOS built with only the minimal feature set, and the other with almost all the features. For both cases, names are not part of the build. This feature was removed from the metrics because it is highly probable that shipping products utilizing this RTOS will not include the naming of descriptors, as its usefulness is mainly limited to debugging and making the opening/creation of components run-time safe.

The code size numbers are expressed with "less than" as they have been rounded up to multiples of 25 for the "C" code. These numbers were obtained using the beta release of the RTOS and may change. One should interpret these numbers as the "very likely" numbers for the released version of the RTOS.

The code memory required by the RTOS includes the "C" code and assembly language code used by the RTOS. The code optimization settings of the compiler that were used for the memory measurements are:

| 1 | . Optimization:                | Level 2 (-02) |

|---|--------------------------------|---------------|

| 2 | Optimize for Time:             | Disabled      |

| 3 | Split Load and Store Multiple: | Disabled      |

All other options are disabled as they do not affect the code generated.

| 🛛 Options for Target 'Target 1'                                                                      | ×                                            |

|------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Device   Target   Output   Listing   User C/C++   Asm   Linker   Debug   Utilities                   | ,                                            |

| Preprocessor Symbols                                                                                 |                                              |

| Define:                                                                                              |                                              |

| Undefine:                                                                                            |                                              |

| Language / Code Generation                                                                           |                                              |

| Strict ANSI C                                                                                        | Warnings:                                    |

| Optimization: Level 2 (-O2)  Enum Container always int                                               | <unspecified></unspecified>                  |

| Optimize <u>f</u> or Time     Ime     Plain Char is Signed                                           | Thumb Mode                                   |

| Split Load and Store Multiple Read-Only Position Independent                                         |                                              |

| One <u>E</u> LF Section per Function <u>Read-Write Position Independent</u>                          |                                              |

| Include<br>Paths<br>Misc                                                                             |                                              |

| Controls                                                                                             |                                              |

| Compiler<br>control<br>\CMSIS\Include -I C:\Keil\ARM\Inc\ST\STM32F4xx -o "*.o" -omf_browse<br>string | 1\Inc -I C:\Keil\ARM<br>e "*.cf"depend "*.d" |

| OK Cancel Defaults                                                                                   | Help                                         |

Figure 7-1 Memory Measurement Code Optimization Settings

| Description                                         | Code Size    |

|-----------------------------------------------------|--------------|

| Minimal Build                                       | < 650 bytes  |

| + Runtime service creation / static memory          | < 850 bytes  |

| + Multiple tasks at same priority                   | < 925 bytes  |

| + Runtime priority change                           | < 1375 bytes |

| + Mutex priority inheritance                        |              |

| + FCFS                                              |              |

| + Task suspension                                   |              |

| + Timer & timeout                                   | < 1800 bytes |

| + Timer call back                                   |              |

| + Round robin                                       |              |

| + Events                                            | < 2400 bytes |

| + Mailbox                                           |              |

| Full Feature Build (no names)                       | < 2875 bytes |

| Full Feature Build (no names / no runtime creation) | < 2525 bytes |

| Full Feature Build (no names / no runtime creation) | < 2825 bytes |

| + Timer services module                             |              |

#### Table 7-1 "C" Code Memory Usage

Table 7-2 Assembly Code Memory Usage

| Description                                | Size       |

|--------------------------------------------|------------|

| Assembly code size (FPU OFF)               | 176 bytes  |

| Assembly code size (FPU ON)                | 268 bytes  |

| Vector table (per interrupt handler entry) | +4 bytes   |

| Hybrid Stack Enabled                       | +12 bytes  |

| Saturation Bit Enabled                     | +24 bytes  |

| FPU runtime ON / OFF                       | +180 bytes |

There are two aspects when describing the data memory usage by the RTOS. First, the RTOS needs its own data memory to operate, and second, most of the services offered by the RTOS require data memory for each instance of the service. As the build options affect either the kernel memory needs or the service descriptors (or both), an interactive calculator has been made available on Code Time Technologies website.

### 7.2 Latency

Latency of operations has been measured on a Olimex STM32-P407 Evaluation board populated with a 168 MHz STM32F407 device. The clock setting for the measurement used the internal oscillator operating at 16 MHz, which allows running from the flash with 0 wait states. All measurements have been performed on the real platform. This means the interrupt latency measurements had to be instrumented to read the SysTick counter value. This instrumentation can add up to 5 or 6 cycles to the measurements. The code optimization settings that were used for the latency measurements are:

| 1. | Optimization:                  | Level 3 (-03) |

|----|--------------------------------|---------------|

| 2. | Optimize for Time:             | Enabled       |

| 3. | Split Load and Store Multiple: | Disabled      |

All other options are disabled, as they do not affect the efficiency of the code generated.

| Options for node "Demo                                                                                                                                                                                                                                                                                                    | _1_CORTEXM3_IAR"                                                                                   | ×                                                                                                                                                                                                                                                                                                                     |